这种方法在过去需要两个独立的开发团队,这会增加非重复性工程成本、开发与技术风险。此外,该方法还将设计功能固定在处理器内核或可编程逻辑中,使后期优化难以进行。人们所需的开发工具应该可实现整个器件的软件定义开发,并有能力根据需要将功能从处理器内核转移到可编程逻辑,而且非HDL专家也能完成。这正是系统优化编译器的用武之地。系统优化编译器能利用C、C++或OpenCL™等高级语言以软件方式定义整个系统行为。然后,使用系统优化编译器执行处理器系统与可编程逻辑之前的功能分区,该编译器能够使功能无缝移动,以便选择是在处理器系统中运行还是在可编程逻辑中实现。图1-使用系统优化编译器选择要加速的功能。通过使用处理系统内部的内置定时器来为功能执行计时。

可找出造成瓶颈的功能,从而创建瓶颈功能。这些瓶颈功能便成为候选,以备通过使用系统优化编译器在可编程逻辑中实现加速。处理系统与可编程逻辑之间的移动是通过系统优化编译器的高层次综合(可将C、C++、OpenCL程序转换为Verilog或VHDL描述的工具)与软件定义连接框架之间的结合来实现的。软件定义连接框架能够无缝地将HLS结果连接至软件应用,设计团队使用这种方法,一键就能在处理器和可编程逻辑间移动功能。当然在用户把功能移动到可编程逻辑时,他们也得到了明显的性能提升,自然这是使用可编程逻辑的结果。与CPU/GPU解决方案相比,在PL中进行加速还能提高确定性并降低时延,这对诸如ECU和ADAS的应用来说是至关重要的。

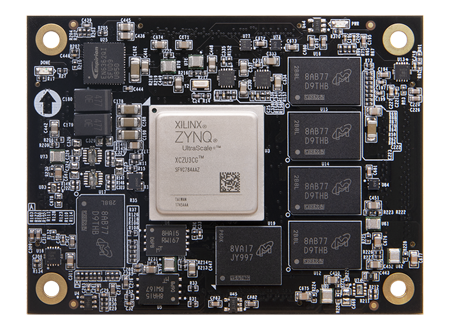

图2-XC6SLX25T-3CSG324I 使用系统优化编译器对资源与性能进行估算。很多汽车应用都是使用业界标准开源库进行开发,例如在ADAS系统中使用OpenCV或Caffe,或在ECU中使用标准数学库。为加快这些应用的开发,系统优化编译器需要能够支持多个HLS库,以便开发人员在其应用中使用。系统优化编译器应支持多个关键库,·数学库–提供标准数学库的可综合实现。·IP库–为实现FFT、FIR和移位寄存器LUT功能提供IP库。·线性代数库–提供通用线性代数功能库。·任意精度数据类型库–使用有符号和无符号整数支持非2次幂的任意长度数据。该库允许开发人员更高效地使用FPGA资源。这些库的提供为开发团队提供相当大的支持,让开发团队不必开发类似的功能。

EP3SL50F484C2N, XC4003E-3PQ100C, XC6VLX195T-2FFG784C,

EP3SL50F484I3N, XC4003E-4PC84C, XC6VLX195T-3FFG1156C,

EP3SL70F484I4, XC4005-4PQ160C, XC6VLX195T-L1FFG784I,

EP4C10F17C8N, XC4005-6PG156M, XC6VLX240T-1FF1156I,

EP4CE10E22C6N, XC4005E-3PQ100I, XC6VLX240T-1FF784I,

EP4CE10E22C8N, XC4005E-3TQ144C, XC6VLX240T-1FFG1156C,

EP4CE10E22C8N , XC4005E-4PC84C, XC6VLX240T-1FFG1156I,

EP4CE10E22I7, XC4005E-4PC84I, XC6VLX240T-1FFG1759C,

EP4CE10E22I7N, XC4005E-4PG156I, XC6VLX240T-1FFG1759I,

EP4CE10E22I8LN, XC4005E-4PG156M, XC6VLX240T-1FFG784C,

EP4CE10F17C6N, XC4005E-4PQ160I, XC6VLX240T-1FFG784I,

EP4CE10F17C7N, XC4005E-7TQ144C, XC6VLX240T-2FF1156C,

EP4CE10F17C8N, XC4005XL-2PQ100C, XC6VLX240T-2FF1156I,

EP4CE10F17C8N , XC4005XL-3PQ100C, XC6VLX240T-2FF1759I,

EP4CE10F17I7, XC4005XL-3TQ144C, XC6VLX240T-2FFG1156,

EP4CE10F17I7N, XC4006E-3PQ160C, XC6VLX240T-2FFG1156C,

EP4CE10F17I7N , XC4006E-3TQ144I, XC6VLX240T-2FFG1156I,

EP4CE10F17I8LN, XC4006E-4PQ160C, XC6VLX240T-2FFG1759I,

EP4CE10U14I7N, XC4006E-4PQ208I, XC6VLX365T-1FFG1156C,

EP4CE115F23C7N, XC4006E-4TQ144C, XC6VLX365T-1FFG1156I。