AT25SF081B-MAHD-T 产品概述 Adesto® AT25SF081B 是一款串行接口闪存设备,专为各种大容量消费类应用而设计,在这些应用中,程序代码从闪存中复制到嵌入式或外部 RAM 中以供执行。

AT25SF081B 的灵活擦除架构也非常适合数据存储,

无需额外的数据存储设备。AT25SF081B 擦除块大小经过优化,可满足当今代码和数据存储应用的需求。这意味着可以更有效地使用内存空间。

由于某些代码模块和数据存储段必须驻留在自己的擦除区域中,因此可以大大减少大块擦除闪存设备中浪费和未使用的内存空间。

这种增加的内存空间允许添加额外的代码例程和数据存储段,同时保持相同的整体设备密度。

该设备还包含三个安全寄存器页面,用于独特的设备序列化、系统级电子

AT25SF081B-MAHD-T 主要特性

兼容串行外设接口 (SPI) 支持 SPI 模式 0 和 3 (1,1,1)

支持双输入和双输出操作 (1,1,2) 支持四输入和四输出操作 (1,1,4)

支持四 XiP(连续读取模式)操作(1,4,4 和 0,4,4) 最大工作频率为 108 MHz

提供两种选项: 2.7 V ~ 3.6 V 电源电压 2.5 V ~ 3.6 V 电源电压 支持串行闪存可发现参数 (SFDP、JDES216B)

OTP 存储器 三个受保护的可编程安全寄存器页(页大小:256 字节)

64 位工厂可编程 UID 寄存器 硬件写保护(WP 引脚) 软件写保护(可编程非易失性控制寄存器)

编程和擦除暂停和恢复 字节编程大小:最多 256 字节 擦除大小和持续时间统一的 4 KB 块擦除(典型值 70 ms)

统一的 32 KB 块擦除(典型值 150 ms) 统一的 64 KB 块擦除(典型值 250 ms) 全芯片擦除(典型值 4 秒)

低功耗 待机电流(25

产品属性 属性值 选择属性

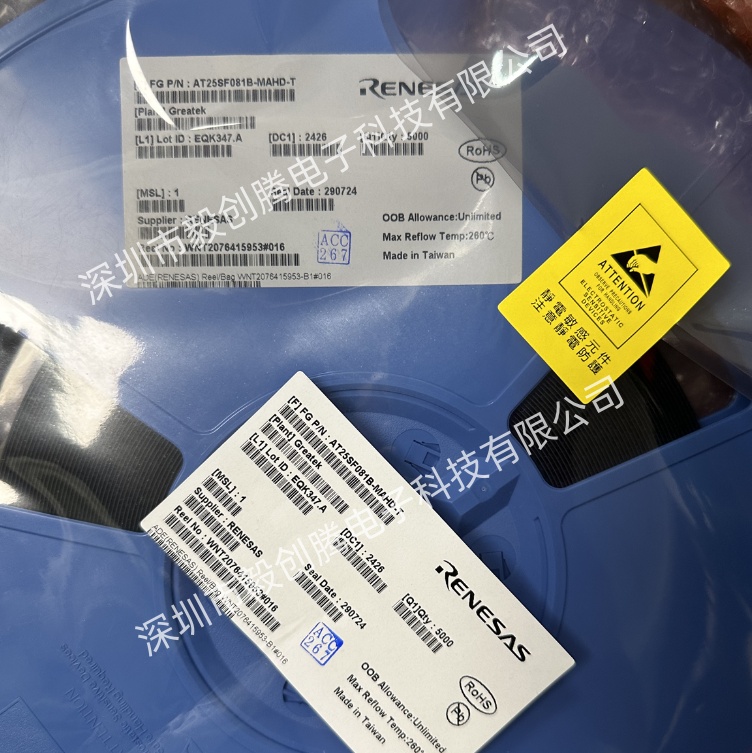

制造商: Renesas Electronics

产品种类: NOR闪存

RoHS: 详细信息

安装风格: SMD/SMT

封装 / 箱体: UDFN-8

系列: AT25SF081B

封装: Reel

封装: Cut Tape

商标: Renesas / Dialog

产品类型: NOR Flash

5000

子类别:Memory & Data Storage

设备操作AT25SF081B 由主机控制器 SPI Master 发送的一组指令控制。SPI Master 通过 SPI 总线与 AT25SF081B 通信,该总线由四个引脚组成:片选 (CS)、串行时钟 (SCK)、

串行输入 (SI) 和串行输出 (SO)。SPI 协议定义了总共四种操作模式(模式 0、1、2 或 3)。AT25SF081B 支持两种最常见的模式,即 SPI 模式 0 和 3。

对于这些模式,数据在 SCK 的上升沿锁存,并在 SCK 的下降沿输出。图 4:SPI 模式 0 和 35.1 双输出读取 (1-1-2)AT25SF081B 具有双输出读取模式,

允许每个时钟周期从设备输出两位数据以提高吞吐量。为此,SI 和 SO 引脚都用作传输数据字节的输出。使用双输出读取阵列命令,SI 引脚与 SO 引脚一起成为输出。

5.2 双 I/O 读取 (1-2-2)AT25QF128A 支持双 I/O (1-2-2) 传输,可提高吞吐量

读取阵列命令可用于在指定初始起始地址后通过提供时钟引脚来顺序读取器件中的连续数据流。器件包含一个内部地址计数器,该计数器在每个时钟周期自动递增。

要执行读取阵列操作,必须先断言 CS 引脚,然后将适当的操作码(0Bh 或 03h)输入器件。输入操作码后,

必须输入三个地址字节以指定要在内存阵列中读取的第一个字节的起始地址位置。如果 0Bh 操作码用于读取阵列操作,则必须在三个地址字节之后将一个额外的虚拟字节输入器件。

输入三个地址字节(如果使用操作码 0Bh,则输入虚拟字节)后,额外的时钟周期会导致数据在 SO 引脚上输出。

数据始终以字节的 MSB 优先输出。当读取完内存阵列的最后一个字节(0FFFFFh)。

毅创腾新到现货:

BTM7741G

NCS2333MUTBG

MBI5039GP-B

SX03-0B00-00

SX07-0B00-02

SX04-0B00-00

AFBR-59E4APZ

CY8C4146AZI-S433

5CGTFD9E5F31I7N

MAX9260GCB/V+T

10M50DAF256C7G

LFE5U-25F-8BG256C

MC9S08AC32CFUER

XCKU5P-2FFVB676I

XCVU7P-2FLVB2104I

CY96F348RSBPMC-GS-UJE2

LTC6813ILWE-1#3ZZTRPBF

XCVU9P-2FLGB2104I3991

XCVU9P-L2FLGA2104E3991

双输出读取阵列命令类似于标准读取阵列命令,一旦指定了初始起始地址,便可通过提供时钟引脚来顺序读取来自设备的连续数据流。

与标准读取阵列命令不同,双输出读取阵列命令允许在每个时钟周期从设备输出两位数据,而不仅仅是一位。要执行双输出读取阵列操作,

必须先断言 CS 引脚;然后,必须将操作码 3Bh 输入设备。输入操作码后,必须输入三个地址字节以指定要在内存阵列中读取的第一个字节的位置。

在三个地址字节之后,还必须将单个虚拟字节输入设备。输入三个地址字节和虚拟字节后,其他时钟周期会在 SO 和 SI 引脚上输出数据。数据首先以字节的 MSB 输出,然后 MSB 在 SO 引脚上输出。